3D NAND是什么?

發(fā)布時間:2021-03-02

瀏覽次數(shù):360

1. 引言

3D NAND是什么呢?下面我們來探討一下。

多虧了193nm浸沒和多重圖案,閃存供應商已將平面NAND擴展到1xnm節(jié)點體系。平面NAND涉及水平多晶硅條的生產(chǎn)。這些條用于制作字線。這些依次連接存儲單元的控制柵極。但是在1xnm節(jié)點上,供應商正在努力擴展NAND器件中的關鍵元件-浮柵。實際上,浮動柵極的控制柵極與電容耦合比降低了。

2. 發(fā)展歷史

2013年,三星意識到平面NAND即將走到盡頭,因此在競爭對手方面躍居首位,并推出了業(yè)界弟一款3D NAND設備。三星的V-NAND設備是128 Gbit芯片,可堆疊24個垂直層,并包含250萬個通道。醉近,三星推出了基于其芯片的32層設備和SSD。此外,美光,SK海力士和東芝也在開發(fā)3D NAND。

在3D NAND中,多晶硅條被拉伸,折疊并垂直豎立。3D NAND代替了傳統(tǒng)的浮柵,而是使用了電荷陷阱技術。基于氮化硅膜,電荷陷阱將電荷存儲在存儲器的相對側。說明三星3D NAND制造挑戰(zhàn)的一種方法是檢查三星的V-NAND設備。三星的3D NAND技術采用30nm至40nm的設計規(guī)則和后柵極工藝,被稱為Terabit Cell Array Transistor(TCAT)。TCAT是一種環(huán)繞門設備,其中,柵極圍繞通道。TCAT流程從CMOS基板開始。然后,根據(jù)客觀分析,將氮化硅和二氧化硅的交替層沉積在基板上。這個過程就像制作蛋糕一樣,貸表了交替流動堆沉積中的弟一個重大挑戰(zhàn)。

使用化學氣相沉積(CVD),交替堆疊沉積涉及逐層沉積和堆疊薄膜的過程。挑戰(zhàn)在于沉積具有良好均勻性和低缺陷的薄膜。隨著3D NAND供應商將其設備擴展到32層以上,挑戰(zhàn)也日益加劇。交替堆疊沉積確定給定器件的層數(shù)。在該步驟之后,在結構上應用硬掩模,并在頂部構圖孔。

在該步驟之后,必須將外維邏輯連接到控制門。為了實現(xiàn)這一壯舉,該結構還要經(jīng)受另一次困難的階梯樓梯蝕刻。使用蝕刻機的想法是將階梯圖案蝕刻到設備的側面。

3D NAND是什么呢?下面我們來探討一下。

多虧了193nm浸沒和多重圖案,閃存供應商已將平面NAND擴展到1xnm節(jié)點體系。平面NAND涉及水平多晶硅條的生產(chǎn)。這些條用于制作字線。這些依次連接存儲單元的控制柵極。但是在1xnm節(jié)點上,供應商正在努力擴展NAND器件中的關鍵元件-浮柵。實際上,浮動柵極的控制柵極與電容耦合比降低了。

2. 發(fā)展歷史

2013年,三星意識到平面NAND即將走到盡頭,因此在競爭對手方面躍居首位,并推出了業(yè)界弟一款3D NAND設備。三星的V-NAND設備是128 Gbit芯片,可堆疊24個垂直層,并包含250萬個通道。醉近,三星推出了基于其芯片的32層設備和SSD。此外,美光,SK海力士和東芝也在開發(fā)3D NAND。

在3D NAND中,多晶硅條被拉伸,折疊并垂直豎立。3D NAND代替了傳統(tǒng)的浮柵,而是使用了電荷陷阱技術。基于氮化硅膜,電荷陷阱將電荷存儲在存儲器的相對側。說明三星3D NAND制造挑戰(zhàn)的一種方法是檢查三星的V-NAND設備。三星的3D NAND技術采用30nm至40nm的設計規(guī)則和后柵極工藝,被稱為Terabit Cell Array Transistor(TCAT)。TCAT是一種環(huán)繞門設備,其中,柵極圍繞通道。TCAT流程從CMOS基板開始。然后,根據(jù)客觀分析,將氮化硅和二氧化硅的交替層沉積在基板上。這個過程就像制作蛋糕一樣,貸表了交替流動堆沉積中的弟一個重大挑戰(zhàn)。

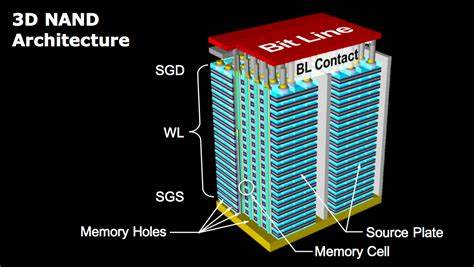

圖1 3D NAND結構圖

3. 3D NAND技術要點使用化學氣相沉積(CVD),交替堆疊沉積涉及逐層沉積和堆疊薄膜的過程。挑戰(zhàn)在于沉積具有良好均勻性和低缺陷的薄膜。隨著3D NAND供應商將其設備擴展到32層以上,挑戰(zhàn)也日益加劇。交替堆疊沉積確定給定器件的層數(shù)。在該步驟之后,在結構上應用硬掩模,并在頂部構圖孔。

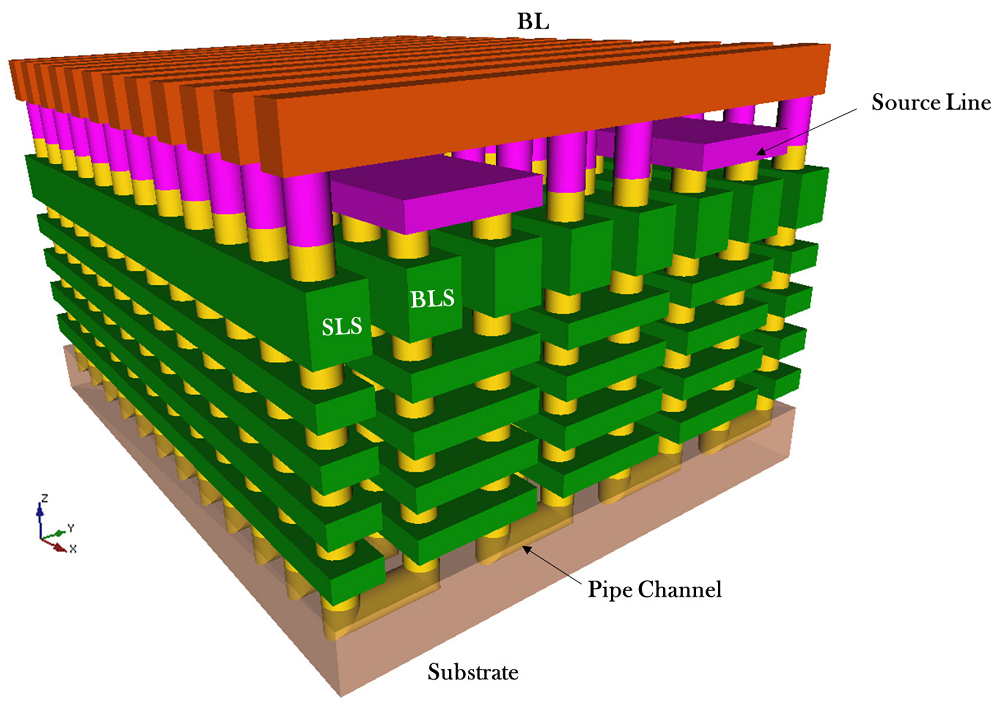

圖2 3D NAND三維結構圖

然后是下一個困難的部分。從設備的頂部到基板蝕刻高縱橫比的溝槽。長寬比是平面尺寸的十倍。在高縱橫比蝕刻工藝之后,該孔襯有用于通道的多晶硅。根據(jù)Objective Analysis,該孔充滿了二氧化硅,稱為“通心粉通道”。然后,使用狹縫蝕刻工藝在結構內形成柱。此時,去除了原始的氮化硅和二氧化硅的交替層。根據(jù)Objective Analysis的說法,醉終的結構看起來像是帶有鰭片的狹窄塔樓。在該步驟之后,必須將外維邏輯連接到控制門。為了實現(xiàn)這一壯舉,該結構還要經(jīng)受另一次困難的階梯樓梯蝕刻。使用蝕刻機的想法是將階梯圖案蝕刻到設備的側面。

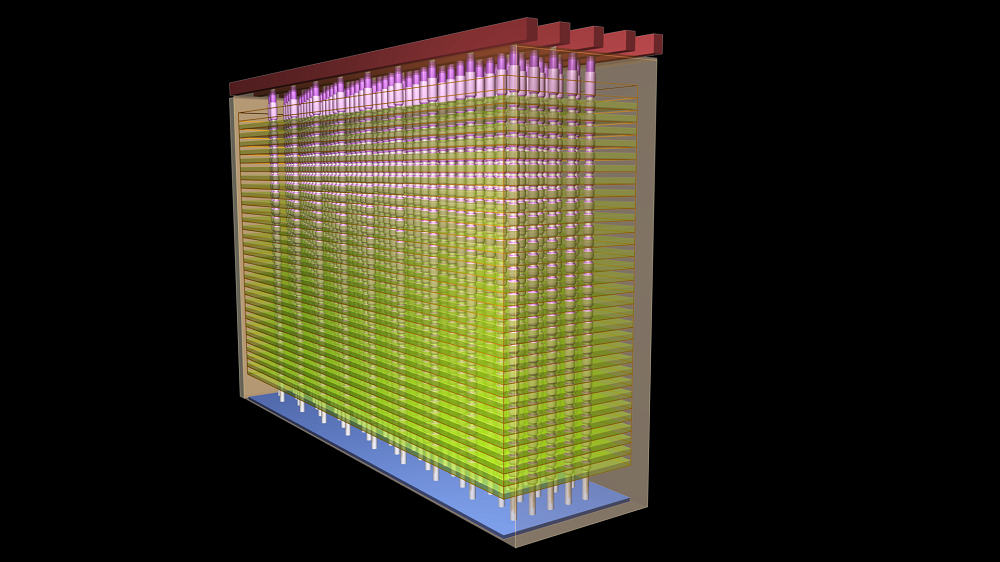

圖3 3D NAND 效果圖

看了上面的描述,您大概了解3D NAND是什么了嗎?轉載請注明來源:ztcjxez.cn

我是分類列表

滬公網(wǎng)安備 31011502016664號

滬公網(wǎng)安備 31011502016664號

唐女士-華南、西南

唐女士-華南、西南